1. Jurnal [Kembali]

2. Alat dan Bahan

[Kembali]

a.Panel DL 2203D

b.Panel DL 2203C

c.Panel DL 2203S

Gambar 1. Modul De Lorenzo

d. Jumper

e. IC 4013

3. Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

Rangkaian terdiri dari 4 buah IC JK Flip FLop Yng saling berhubungan. Masing2 swicth merepresentasikan Input pada IC.

Pada rangkaian ini merupakan rangkaian SISO yang berarti memiiki 1 input masukan dari J-K flip flop pertama dan 1 input keluaran dari J-K flip flop terakhir (ke-4) dimana angka akan bergeser dari bit pertama keluaran hingga bit ke-4 keluaran setiap inputan logika baru yang diinputkan pada inputan IC J-K flip flop pertama, berarti pada rangkaian terjadi perwakilan dari penggeseran masukan suatu biner ke kiri atau ke kanan dimana pergeseran ini akan mewakili MSB dan LSB dari 4 bit binner keluaran. Terjadinya pergeseran input masukan logika pada rangkaian ini juga berarti bahwa proses terjadinya register geser ini dapat menyimpan memori sementara pada saat pergeseran masukan menuju keluaran bit ke-4 dari dearah lingkup keluaran 4 bit.

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

- Analisa output yang dihasilkan tiap-tiap kondisi!

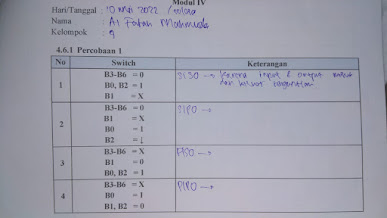

- Untuk kondisi yang pertama, jenis shift register yang dihasilkan yaitu SISO karena input dan outputnya masuk dan keluar bergantian.

- Untuk kondisi kedua, jenis shift register yang dihasilkan yaitu SIPO karena inputnya masuk bergantian dan outputnya keluar bersamaan.

- Untuk kondisi ketiga, jenis shift register yang dihasilkan yaitu PISO karena inputnya masuk bersamaan dan outputnya keluar bergantian.

- Untuk kondisi keempat, jenis shhift register yang dihasilkan yaitu PIPO karena input dan outputnya masuk dan keluar bersamaan.

- Jika gerbang and pada rangkaian dihapus dan dihubungkan langsung ke flip flop, bandingkan output yang dihasilkan!

- Ketika gerbang AND dihilangkan dan clock dihubungkan langsung ke flip flop dan rangkaian dijalankan, clock-nya akan selalu aktif karena tidak ada yang akan membuat clock mati. Gerbang AND disini berfungsi untuk mematikan clock ketika gerbang NAD berlogika 0.

7. Link Download

[Kembali]

Video [disini]

datasheet jk flip-flop [disini]

datasheet IC 4013 [disini]

datasheet SW SPDT [disini]

HTML [disini]

0 komentar:

Posting Komentar